#### Datasheet

#### 1. Features and Benefits

- Triaxis<sup>®</sup> Hall Technology

- Automotive Grade (AEC-Q100)

- Micro-power with Programmable Duty Cycle

- Selectable Digital Output

- 16-bit Magnetic (XYZ)

- 16-bit Supply Voltage (V)

- 14-bit Temperature (T)

- At runtime programmable modes

- Single Measurement

- Burst Mode up to 2kHz (XYZ)

- Wake-up On Change (WOC) Mode

- Programmable Measurement Range & extended magnetic sensing range option

- On-chip magnetic calibration data allowing off-chip DSP to achieve maximum accuracy

- 8-bit measurement CRC

- Measurement Counter

- Selectable Bus Protocol Slave node

- Up to 10MHz SPI or 1MHz I<sup>2</sup>C

- 48-bit unique ID Number

- RoHS Compliant & Green Packages

## 2. Application Examples

- HMI Non-Contacting Potentiometer

- Joystick with Push

- Rotary with Push

- Linear (Long Stroke)

- Top-Column Module

- Stalk Position/Function Sensor

- Center Stack

- Shifter Position Sensor

- Multimedia Rotary/Push Selector

- Knobs / Levers

- Body Control

- Door handle & door lock

- Mirror position

## 3. Description

The MLX90395 Triaxis<sup>®</sup> Magnetic Node is a miniature monolithic sensor IC sensitive to the three orthogonal components of the flux density applied to the IC (i.e. B<sub>X</sub>, B<sub>Y</sub> and B<sub>Z</sub>) and to temperature. This allows the MLX90395 with the correct magnetic circuit to decode the absolute position of any moving magnet. It enables the design of novel generation of non-contacting position sensors that are frequently required for both automotive and industrial applications.

The MLX90395 selectable measurement data can be read over I<sup>2</sup>C or SPI bus. The sensor is runtime programmable and offers on-chip temperature compensation of the measured units. The selectable measurement duty cycle enables unsurpassed micro-power functionality. In this respect, the MLX90395 is the first true Software Defined Sensor: one IC, any magnetic sensing application. You define the function.

## 4. Ordering Information

Note: Ordering code BAA-x0x: not recommended for new designs.

| Product  | Temperature | Package | Option Code | Packing Form | Definition                  |

|----------|-------------|---------|-------------|--------------|-----------------------------|

| MLX90395 | K           | DC      | BAA-000     | RE           | Medium-Field Version (50mT) |

| MLX90395 | K           | GO      | BAA-000     | RE           | Medium-Field Version (50mT) |

| MLX90395 | K           | LW      | BAA-000     | RE           | Medium-Field Version (50mT) |

| MLX90395 | K           | DC      | BAA-100     | RE           | High-Field Version (120mT)  |

| MLX90395 | K           | GO      | BAA-100     | RE           | High-Field Version (120mT)  |

| MLX90395 | K           | LW      | BAA-100     | RE           | High-Field Version (120mT)  |

| MLX90395 | K           | DC      | BBA-001     | RE           | Medium-Field Version (50mT) |

| MLX90395 | K           | GO      | BBA-001     | RE           | Medium-Field Version (50mT) |

| MLX90395 | K           | LW      | BBA-001     | RE           | Medium-Field Version (50mT) |

| MLX90395 | K           | DC      | BBA-101     | RE           | High-Field Version (120mT)  |

| MLX90395 | K           | GO      | BBA-101     | RE           | High-Field Version (120mT)  |

| MLX90395 | K           | LW      | BBA-101     | RE           | High-Field Version (120mT)  |

# Legend:

| Temperature Code:            | K: from -40°C to 125°C                                                  |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Package Code:                | "DC" for SOIC-8 package                                                 |  |  |  |  |

|                              | "GO" for TSSOP-16 package (dual die)                                    |  |  |  |  |

|                              | "LW" for QFN-16 package (wettable flanks)                               |  |  |  |  |

| Option Code - chip revision: | B <b>xx</b> -abc                                                        |  |  |  |  |

|                              | BAA: not recommended for new designs                                    |  |  |  |  |

|                              | B <b>BA</b> : standard version                                          |  |  |  |  |

| Option Code - application:   | Bxx-abc:                                                                |  |  |  |  |

|                              | a: Magnetic Sensing Range                                               |  |  |  |  |

|                              | 0: Medium Field Version (50mT)                                          |  |  |  |  |

|                              | 1: High Field Version (120mT)                                           |  |  |  |  |

|                              | <b>b</b> : N/A                                                          |  |  |  |  |

|                              | c: SPI Filter                                                           |  |  |  |  |

|                              | 0: No filter (SPI frequency up to 10MHz)                                |  |  |  |  |

|                              | 1: 1MHz filter (SPI frequency up to 1MHz)                               |  |  |  |  |

| Packing Form:                | "RE" for Reel                                                           |  |  |  |  |

|                              | "DC": 3000 pcs/reel                                                     |  |  |  |  |

|                              | "GO": 4500 pcs/reel                                                     |  |  |  |  |

|                              | "LW": 5000 pcs/reel                                                     |  |  |  |  |

| Ordering Example:            | "MLX90395KLW-BBA-101-RE"                                                |  |  |  |  |

|                              | For a 120mT sensing range 3D Magnetic Node in QFN-16 package, delivered |  |  |  |  |

|                              | in Reel.                                                                |  |  |  |  |

Table 1: Ordering information

## **Contents**

| 1. Features and Benefits                 | 1  |

|------------------------------------------|----|

| 2. Application Examples                  | 1  |

| 3. Description                           | 1  |

| 4. Ordering Information                  | 2  |

| 5. Functional Diagram                    | 6  |

| 6. Glossary of Terms                     | 8  |

| 7. Pin Definitions                       | 8  |

| 7.1. Pin Definition for SOIC-8 Package   | 8  |

| 7.2. Pin Definition for TSSOP-16 Package | 8  |

| 7.3. Pin Definition for QFN-16 Package   | 9  |

| 8. Absolute Maximum Ratings              | 10 |

| 9. Isolation Specification               | 10 |

| 10. General Description                  | 11 |

| 11. General Electrical Specification     | 12 |

| 12. Timing Specification                 | 14 |

| 13. Temperature Specification            | 15 |

| 14. Voltage Specification                | 15 |

| 15. Magnetic Field Requirements          | 16 |

| 15.1. Medium-Field Variant (-0xx code)   | 16 |

| 15.2. High-Field Variant (-1xx code)     | 16 |

| 16. Accuracy Specification               | 17 |

| 16.1. Medium-Field Variant (-0xx code)   | 17 |

| 16.2. High-Field Variant (-1xx code)     | 18 |

| 17. Functional Description               | 19 |

| 17.1. Operating Modes                    | 19 |

| 17.1.1. Single Measurement               | 19 |

| 17.1.2. Burst Mode                       | 19 |

| 17.1.3. Wake-up on Change Mode           | 20 |

| 17.2. Flow Chart                         | 21 |

| 17.3. Status Byte                        | 22 |

| 17.3.1. Data Ready - DRDY                | 22 |

| 17.3.2. Reset - RST                      | 22 |

Datasheet

|    | 17.3.3. Single Bit Error Corrected - SEC                                | 22 |

|----|-------------------------------------------------------------------------|----|

|    | 17.3.4. Double Bit Error Detected - DED                                 | 22 |

|    | 17.3.5. Overflow - OVF                                                  | 23 |

|    | 17.3.6. Communication Error - CE                                        | 23 |

|    | 17.3.7. Measurement Counter                                             | 23 |

|    | 17.4. Measurement CRC                                                   | 24 |

|    | 17.4.1. CRC calculation                                                 | 24 |

|    | 17.5. Commands                                                          | 25 |

|    | 17.6. SPI Communication                                                 | 25 |

|    | 17.6.1. Command implementation                                          | 27 |

|    | 17.6.2. SPI Timing Specification                                        | 29 |

|    | 17.6.3. EMC filter (not re-programmable) - Not available in BAA version | 29 |

|    | 17.7. I <sup>2</sup> C Communication                                    | 30 |

|    | 17.7.1. Command Implementation                                          | 30 |

|    | 17.7.2. I <sup>2</sup> C Timing Specification                           | 32 |

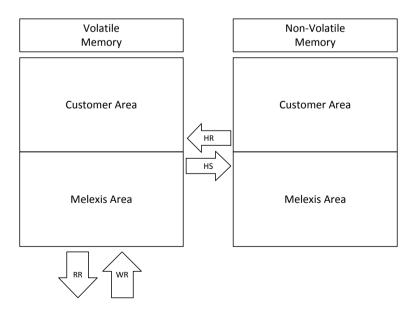

| 18 | 8. Memory Structure and End-User Programmable Items                     | 33 |

|    | 18.1. NVRAM Endurance                                                   | 33 |

|    | 18.2. Memory Structure                                                  | 33 |

|    | 18.3. Register Map                                                      | 34 |

|    | 18.3.1. Default NVRAM content                                           | 36 |

|    | 18.4. Measurement Filters                                               | 37 |

|    | 18.5. Communication and I <sup>2</sup> C Filters                        | 38 |

|    | 18.6. Sensitivity                                                       | 39 |

|    | 18.7. Offset                                                            | 40 |

|    | 18.8. Burst and WOC Parameters                                          | 40 |

|    | 18.9. Thermal Drift                                                     | 40 |

|    | 18.10. External Trigger                                                 | 41 |

|    | 18.11. NVRAM Lock (SPI mode) - Not available in BAA version             | 42 |

|    | 18.11.1. Temporary NVRAM Lock                                           | 42 |

|    | 18.11.2. Permanent NVRAM Lock                                           | 43 |

|    | 18.12. Other Controls                                                   | 43 |

| 19 | 9. Recommended Application Diagrams                                     | 44 |

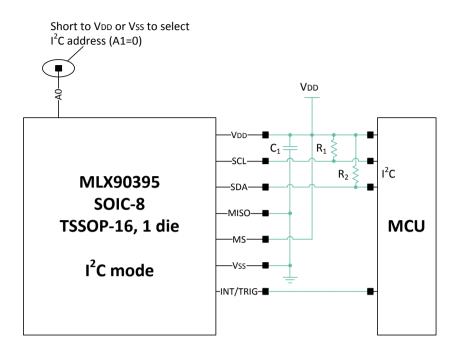

|    | 19.1. Wiring with the MLX90395 in SOIC-8/TSSOP-16 Package               | 44 |

Datasheet

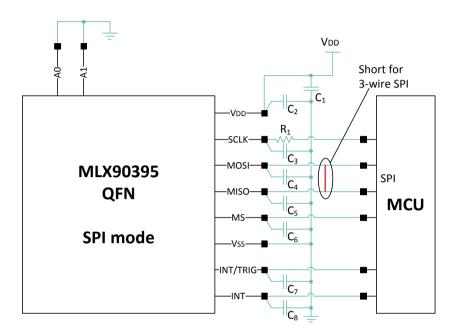

| 19.1.1. SPI Mode                                                                                            | 44  |

|-------------------------------------------------------------------------------------------------------------|-----|

| 19.1.2. I <sup>2</sup> C Mode                                                                               | 46  |

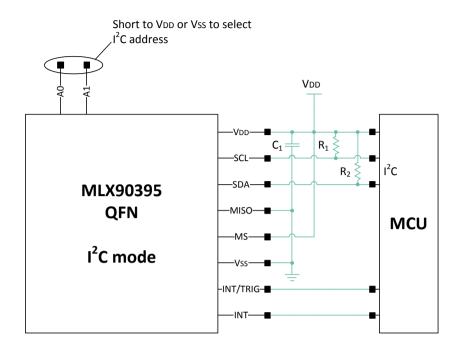

| 19.2. Wiring with the MLX90395 in QFN-16 Package                                                            | 47  |

| 19.2.1. SPI Mode                                                                                            | 47  |

| 19.2.2. I <sup>2</sup> C Mode                                                                               | 49  |

| 20. Standard information regarding manufacturability of Melexis products with different soldering processes |     |

| 21. ESD Precautions                                                                                         | 50  |

| 22. Package Information                                                                                     | 51  |

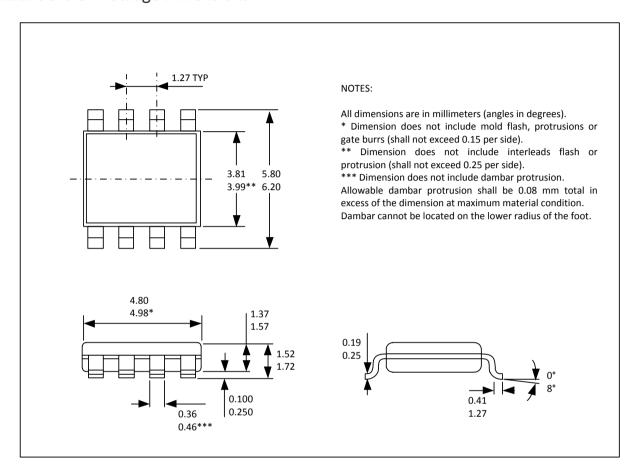

| 22.1. SOIC-8 Package                                                                                        | 51  |

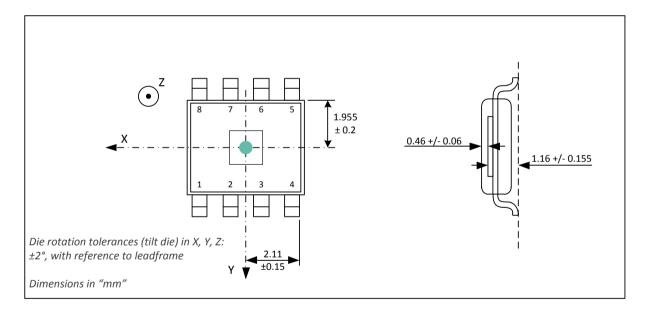

| 22.1.1. SOIC-8 - Package Dimensions                                                                         | 51  |

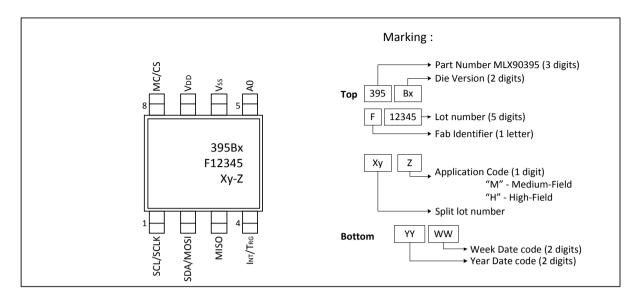

| 22.1.2. SOIC-8 - Pinout and Marking                                                                         | 52  |

| 22.1.3. SOIC-8 - Sensitive Spot Location                                                                    | 52  |

| 22.2. TSSOP-16 Package                                                                                      | 53  |

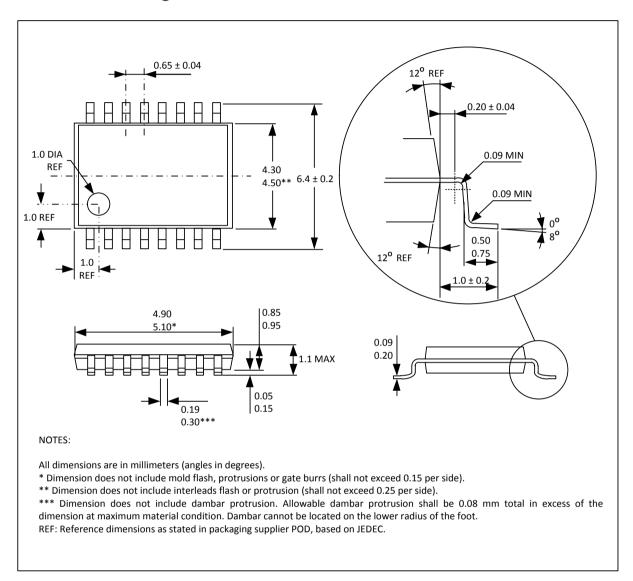

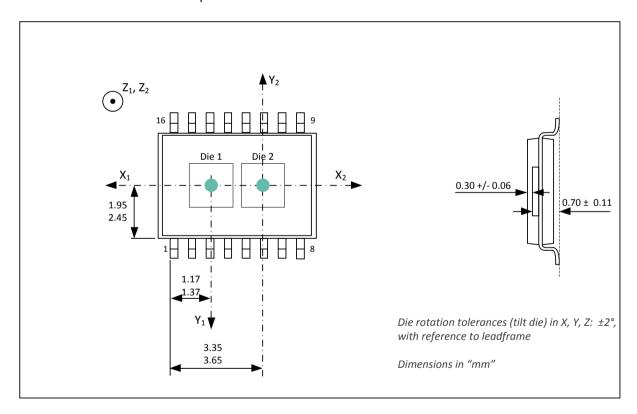

| 22.2.1. TSSOP-16 - Package Dimensions                                                                       | 53  |

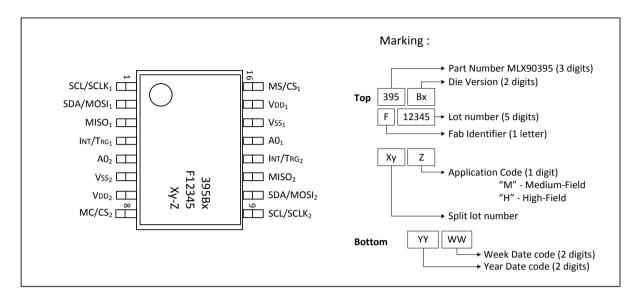

| 22.2.2. TSSOP-16 - Pinout and Marking                                                                       | 54  |

| 22.2.3. TSSOP-16 - Sensitive Spot Location                                                                  | 54  |

| 22.3. QFN-16 Package                                                                                        | 55  |

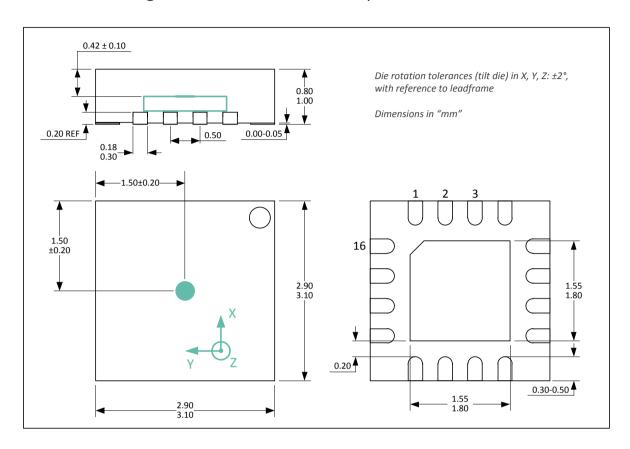

| 22.3.1. QFN-16 - Package Dimensions and Sensitive Spot Location                                             | 55  |

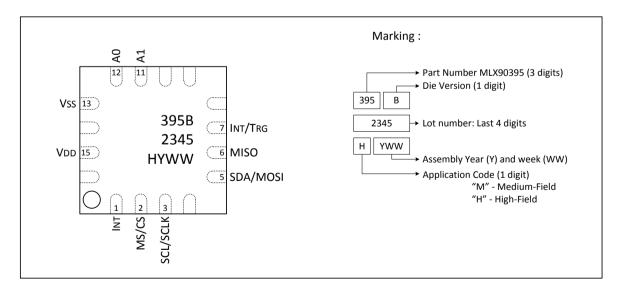

| 22.3.2. QFN-16 - Pinout and Marking (BAA version)                                                           | 55  |

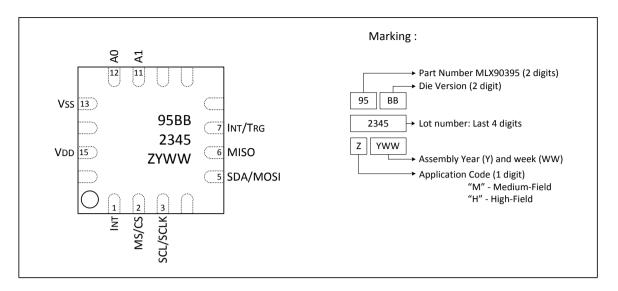

| 22.3.3. QFN-16 - Pinout and Marking (BBA version)                                                           | 56  |

| 22.4. Package Thermal Performances                                                                          | 56  |

| 23. Contact                                                                                                 | 57  |

| 24 Disclaimer                                                                                               | E 7 |

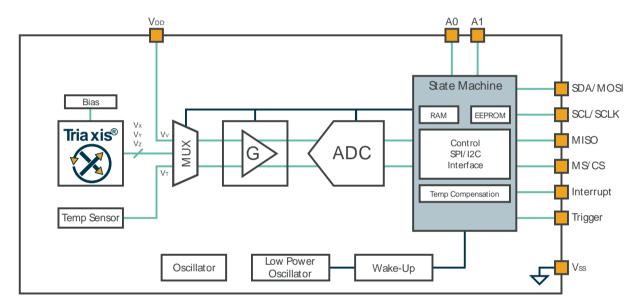

## 5. Functional Diagram

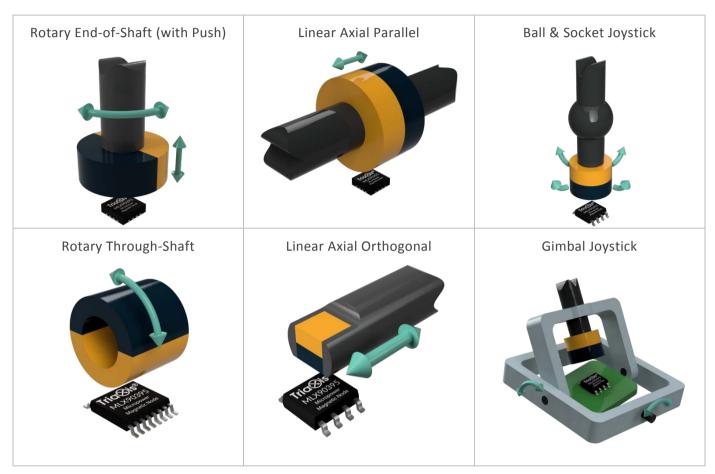

The MLX90395 is sensitive to the three ( $B_X$ ,  $B_Y$ ,  $B_Z$ ) components of the flux density applied to the IC. This allows the MLX90395 with the correct off-chip signal processing to decode the absolute position of any moving magnet (e.g. rotary position from 0 to 360 Degrees, linear displacement, joystick... as shown in Figure 1). The flexibility resides in the runtime selection of measurement data and the application software in the external microcontroller, resulting in a true "Software-Defined Magnetic Sensor".

Figure 1: Magnetic Applications

As the MLX90395 has no on-board microcontroller, it lends itself well to applications requiring a concatenation of multiple sensors on the communication bus of a single microcontroller, allowing more cost-efficient and lean designs. Melexis' Applications Engineers can support in the microcontroller computations.

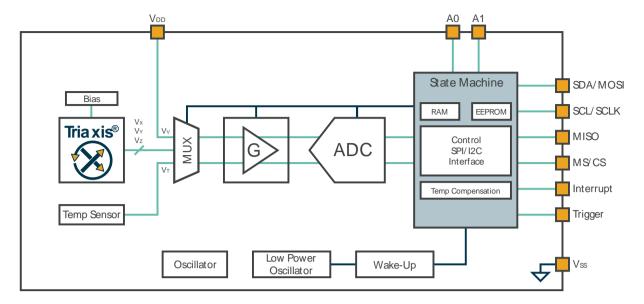

Figure 2: Block Diagram for the QFN-16 package

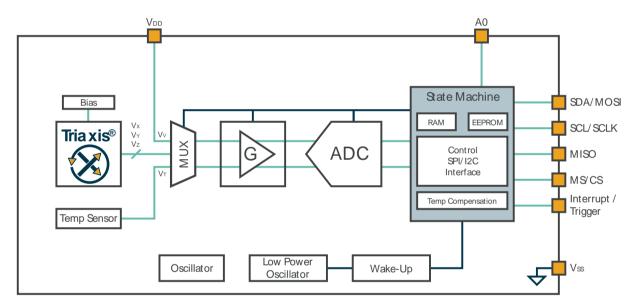

Figure 3: Block diagram for the SOIC-8 (single die) and TSSOP-16 (dual die) package

## 6. Glossary of Terms

| Term                    | Description                                       | Term | Description                      |

|-------------------------|---------------------------------------------------|------|----------------------------------|

| Gauss (G),<br>Tesla (T) | Units for the magnetic flux density:<br>1mT = 10G | EMC  | Electro-Magnetic Compatibility   |

| TC                      | Temperature Coefficient (in ppm/°C)               | FIR  | Finite Impulse Response          |

| ADC                     | Analog-to-Digital Converter                       | OSR  | Over Sampling Rate               |

| DAC                     | Digital-to-Analog Converter                       | PWL  | Piece Wise Linear                |

| LSB                     | Least Significant Bit                             | POR  | Power On Reset                   |

| MSB                     | Most Significant Bit                              | SW   | Software                         |

| DNL                     | Differential Non-Linearity                        | HW   | Hardware                         |

| INL                     | Integral Non-Linearity                            | IMC  | Integrated Magnetic Concentrator |

| ASP                     | Analog Signal Processing                          | ROM  | Read-only Memory                 |

| DSP                     | Digital Signal Processing                         | RAM  | Random-access Memory             |

| CDM                     | Charge Device Model                               | ESD  | Electrostatic Discharge          |

| HBM                     | Human Body Model                                  |      |                                  |

Table 2: Glossary of Terms

## 7. Pin Definitions

## 7.1. Pin Definition for SOIC-8 Package

| Pin # | Name (I <sup>2</sup> C) | Name (SPI) | Description                                     |

|-------|-------------------------|------------|-------------------------------------------------|

| 1     | SCL                     | SCLK       | [I] Bus clock                                   |

| 2     | SDA                     | MOSI       | [I/O] Bus Data / SPI Master Out Slave In        |

| 3     | Not Used                | MISO       | [O] SPI Master In Slave Out                     |

| 4     | INT/TRG                 | INT/TRG    | [O or I] Interrupt / Trigger Pin (Programmable) |

| 5     | A0                      | Not Used   | [I] I <sup>2</sup> C Address Pin 0              |

| 6     | Vss                     | Vss        | [S] Ground                                      |

| 7     | VDD                     | VDD        | [S] Supply                                      |

| 8     | MS                      | /CS        | [I] Mode Select / Chip Select                   |

Table 3: SOIC-8 Pin Definitions and Descriptions

For optimal EMC behaviour connect the unused pins (Not Used) to the Ground (See section 19.1). [I] stands for Input Pin, [O] stands for Output Pin and [S] stands for Supply Pin.

## 7.2. Pin Definition for TSSOP-16 Package

| Pin # | Name (I <sup>2</sup> C) | Name (SPI)           | Description                                           |

|-------|-------------------------|----------------------|-------------------------------------------------------|

| 1     | SCL <sub>1</sub>        | SCLK <sub>1</sub>    | [I] Bus clock                                         |

| 2     | SDA <sub>1</sub>        | MOSI <sub>1</sub>    | [I/O] I <sup>2</sup> C Data / SPI Master Out Slave In |

| 3     | Not Used                | $MISO_1$             | [O] SPI Master In Slave Out                           |

| 4     | INT/TRG <sub>1</sub>    | INT/TRG <sub>1</sub> | [O or I] Interrupt / Trigger Pin (Programmable)       |

| 5     | $A0_2$                  | Not Used             | [I] I <sup>2</sup> C Address Pin 0                    |

| 6     | VSS <sub>2</sub>        | VSS <sub>2</sub>     | [S] Ground                                            |

| 7     | VDD <sub>2</sub>        | VDD <sub>2</sub>     | [S] Supply                                            |

| 8     | MS <sub>2</sub>         | /CS <sub>2</sub>     | [I] Mode Select / Chip Select                         |

| 9     | SCL <sub>2</sub>        | SCLK <sub>2</sub>    | [I] Bus clock                                         |

| Pin # | Name (I <sup>2</sup> C) | Name (SPI)           | Description                                           |

|-------|-------------------------|----------------------|-------------------------------------------------------|

| 10    | SDA <sub>2</sub>        | MOSI <sub>2</sub>    | [I/O] I <sup>2</sup> C Data / SPI Master Out Slave In |

| 11    | Not Used                | MISO <sub>2</sub>    | [O] SPI Master In Slave Out                           |

| 12    | INT/TRG <sub>2</sub>    | INT/TRG <sub>2</sub> | [O or I] Interrupt / Trigger Pin (Programmable)       |

| 13    | $A0_1$                  | Not Used             | [I] I <sup>2</sup> C Address Pin 0                    |

| 14    | VSS <sub>1</sub>        | VSS <sub>1</sub>     | [S] Ground                                            |

| 15    | $VDD_1$                 | $VDD_1$              | [S] Supply                                            |

| 16    | $MS_1$                  | /CS <sub>1</sub>     | [I] Mode Select / Chip Select                         |

Table 4: TSSOP-16 Pin Definitions and Descriptions

For optimal EMC behaviour connect the unused pins (Not Used) to the Ground (See section 19.1). [I] stands for Input Pin, [O] stands for Output Pin and [S] stands for Supply Pin.

## 7.3. Pin Definition for QFN-16 Package

| Pin # | Name (I <sup>2</sup> C) | Name (SPI) | Description                                           |

|-------|-------------------------|------------|-------------------------------------------------------|

| 1     | INT                     | INT        | [O] Interrupt                                         |

| 2     | MS                      | /CS        | [I] Mode Select / Chip Select                         |

| 3     | SCL                     | SCLK       | [I] Bus clock                                         |

| 4     | Not Used                | Not Used   | Not Connected                                         |

| 5     | SDA                     | MOSI       | [I/O] I <sup>2</sup> C Data / SPI Master Out Slave In |

| 6     | Not Used                | MISO       | [O] SPI Master In Slave Out                           |

| 7     | INT/TRG                 | INT/TRG    | [O or I] Interrupt / Trigger Pin (Programmable)       |

| 8     | Not Used                | Not Used   | Not Connected                                         |

| 9     | Not Used                | Not Used   | Not Connected                                         |

| 10    | Not Used                | Not Used   | Not Connected                                         |

| 11    | A1                      | Not Used   | [I] I <sup>2</sup> C Address Pin 1                    |

| 12    | A0                      | Not Used   | [I] I <sup>2</sup> C Address Pin 0                    |

| 13    | Vss                     | Vss        | [S] Ground                                            |

| 14    | Not Used                | Not Used   | Not Connected                                         |

| 15    | VDD                     | VDD        | [S] Supply                                            |

| 16    | Not Used                | Not Used   | Not Connected                                         |

Table 5: QFN-16 Pin Definitions and Descriptions

For optimal EMC behaviour connect the unused pins (Not Used) to the Ground (See section 19.2). [I] stands for Input Pin, [O] stands for Output Pin and [S] stands for Supply Pin.

## 8. Absolute Maximum Ratings

| Parameter                  | Symbol              | Min. | Тур. | Max. | Unit | Condition                                     |

|----------------------------|---------------------|------|------|------|------|-----------------------------------------------|

| Supply Voltage             | $VDD_{MAX}$         |      |      | 4    | V    | <48h                                          |

| Reverse Voltage Protection | $VDD_{REV}$         | -0.3 |      |      | V    | <48h                                          |

| Positive Output Voltage    | Vout                |      |      | 4    | V    | <48h<br>Vout <vdd+0.3v< td=""></vdd+0.3v<>    |

| Negative Output Voltage    | Vout <sub>REV</sub> | -0.3 |      |      | V    | <48h                                          |

| Positive Input Voltage (1) | Vin                 |      |      | 4    | V    | <48h<br>Vin <vdd+0.3v< td=""></vdd+0.3v<>     |

| Negative Input Voltage     | Vin <sub>REV</sub>  | -0.3 |      |      | V    | <48h                                          |

| Operating Temperature      | T <sub>AMB</sub>    | -40  |      | +125 | °C   | Refer to the qualification profile            |

| Junction Temperature       | T <sub>J</sub>      |      |      | +150 | °C   |                                               |

| Storage Temperature        | $T_{ST}$            | -40  |      | +150 | °C   | Refer to the qualification profile            |

| Magnetic Flux Density      | B <sub>MAX</sub>    | -1   |      | +1   | T    |                                               |

| ESD voltage, HBM           | $ESD_HBM$           | -2   |      | +2   | kV   | According AEC-Q100-002 DC and LW package code |

| ESD voltage, CDM           | ESD <sub>CDM</sub>  | -750 |      | +750 | V    | According AEC-Q100-011 DC and LW package code |

Table 6: Absolute Maximum Ratings

Exceeding the absolute maximum ratings may cause permanent damage. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

## 9. Isolation Specification

Only valid for the package code GO, i.e. TSSOP-16 package (dual die).

| Parameter            | Symbol            | Min. | Тур. | Max. | Unit | Condition                                                                           |

|----------------------|-------------------|------|------|------|------|-------------------------------------------------------------------------------------|

| Isolation Resistance | R <sub>ISOL</sub> | 4    |      |      | ΜΩ   | Between dies, measured between VSS <sub>1</sub> and VSS <sub>2</sub> with ±20V bias |

Table 7: Isolation Specification

<sup>&</sup>lt;sup>1</sup> For shared [I/O] pin, maximum rating for output applies.

### 10. General Description

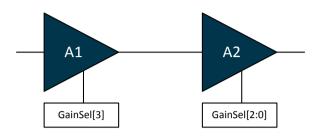

As described on the block diagram the three vector components of the magnetic flux density ( $B_X$ ,  $B_Y$  and  $B_Z$ ) applied to the IC are sensed through the sensor front-end. The respective Hall signals ( $V_X$ ,  $V_Y$  and  $V_Z$ ) are generated at the Hall plates and amplified.

The analog front-end is based on a fully differential analog chain featuring the classic offset cancellation technique (Hall plate 4 Phases spinning and chopper-stabilized amplification).

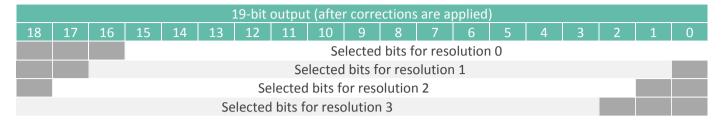

The conditioned analog signals are converted through a sigma-delta ADC (19 bits) and provided to a DSP block for further processing. The DSP stage is a custom finite state machine whose primary function consists of signal conditioning of the raw XYZ signals: offset & sensitivity adjustment and thermal offset & sensitivity drift compensation using the calibrated on-board temperature sensor. The result of these computations are a predetermined transfer characteristic of the sensor for a fixed gain setting.

These 3D linear Hall measurements are made available to the communication bus master for readout. The supported communication protocols are both  $I^2C$  and SPI, where the Triaxis<sup>®</sup> Magnetic Node is a slave on the bus. Upon readback, it is then up to the microcontroller to process the measurement data – either in a vectorial or a scalar way – in order to achieve more complex position sensing functionality required by the application.

When processing data in a vectorial (or angular) way, all signal amplitude variations due to the sensitivity imperfections of the sensor, as well as the flux density degradation of the permanent magnet over temperature are cancelled out. The magnetic vectorial information is intrinsically self-compensated vs. flux density variations. This feature allows therefore an improved thermal accuracy vs. position sensors based on conventional 1D linear Hall sensors.

Another advantage of vectorial versus scalar signal processing is extended absolute position sensing range and higher linearity for Axial Parallel linear stroke position sensing applications.

In addition to the improved thermal accuracy, the realized position sensor features excellent linearity performances taking into account typical manufacturing tolerances (e.g. relative placement between the Hall IC and the magnet).

## 11. General Electrical Specification

General electrical specifications are valid for temperature range: -40 - 125°C, supply voltage range: 2.6/3.0 - 3.6V unless otherwise noted (condition).

| Parameter                                          | Symbol                 | Min. | Тур.       | Max.                   | Unit     | Condition                                           |

|----------------------------------------------------|------------------------|------|------------|------------------------|----------|-----------------------------------------------------|

| Analog Supply Voltage                              | VDD                    | 2.6  | 3.3        | 3.6                    | V        | T <sub>A</sub> ≤ 90°C                               |

| Analog Supply Voltage                              | VDD                    | 3.0  | 3.3        | 3.6                    | V        | $T_A > 90$ °C                                       |

| Supply Current (2)                                 | Idd.conv <sub>XY</sub> |      | 2.3        | 3                      | mA       | X-/Y-axis measurement                               |

| Supply Current <sup>(2)</sup>                      | Idd.conv <sub>z</sub>  |      | 3          | 4                      | mA       | Z-axis measurement                                  |

| Supply Current (2)                                 | Idd.conv <sub>T</sub>  |      | 1.6        | 2                      | mA       | Temperature measurement                             |

| Supply Current (2)                                 | Idd.conv <sub>V</sub>  |      | 1.6        | 2                      | mA       | Voltage measurement                                 |

| Idle Current (2, 3)                                | Idd.idle               |      | 1.4<br>1.4 | 9 <sup>(5)</sup><br>20 | μA<br>μA | $T_A \le 85^{\circ}C$ $T_A$ within $T_{AMB}$        |

| Standby Current (2, 4)                             | Idd.stby               |      | 2.4        | 10 <sup>(5)</sup>      | μΑ<br>μΑ | $T_A \le 85^{\circ}C$ $T_A \text{ within } T_{AMB}$ |

| Surge Current (2, 5)                               | Isurge                 |      | 25         | 250                    | mA       | Startup current, <3µs                               |

| Power-On reset (rising)                            | VporLH                 |      | 1.45       | 1.52                   | V        |                                                     |

| Power-On reset (falling)                           | VporLH                 | 1.3  | 1.39       |                        | V        |                                                     |

| Input High Threshold (5)                           | VIH                    |      |            | 75                     | %VDD     | SDA/MOSI, SCL/SCLK                                  |

| Input Low Threshold (5)                            | VIL                    | 25   |            |                        | %VDD     | SDA/MOSI, SCL/SCLK                                  |

| Input Level Hysteresis <sup>(5)</sup>              | VIHYST                 | 15   | 27         |                        | %VDD     | SDA/MOSI, SCL/SCLK                                  |

| Input High Threshold <sup>(5)</sup>                | VIH                    |      |            | 70                     | %VDD     | INT/TRG, MS/CS                                      |

| Input Low Threshold <sup>(5)</sup>                 | VIL                    | 20   |            |                        | %VDD     | INT/TRG, MS/CS                                      |

| Input Level Hysteresis <sup>(5)</sup>              | VIHYST                 | 17   | 22         |                        | %VDD     | INT/TRG, MS/CS                                      |

| Input Capacitance <sup>(5)</sup>                   | Cin                    |      | 5          | 30                     | pF       |                                                     |

| Output Level High                                  | VOH                    | 98   |            |                        | %VDD     | MISO, INT, INT/TRIG, SDA (Static, 1mA load)         |

| Output Level Low                                   | VOL                    |      |            | 2                      | %VDD     | MISO, INT, INT/TRIG, SDA (Static, 1mA load)         |

| ON Resistance (5)                                  | Rds.on                 | 4    | 6          | 9                      | Ω        | SDA                                                 |

| ON Resistance (5)                                  | Rds.on                 | 13   | 20         | 27                     | Ω        | INT (NMOS and PMOS)                                 |

| Output High Short Circuit<br>Current (5)           | IshortH                | -60  |            |                        | mA       | Vout forced to 0V                                   |

| Output Low Short Circuit<br>Current <sup>(5)</sup> | IshortL                |      |            | 110                    | mA       | Vout forced to VDD                                  |

<sup>&</sup>lt;sup>2</sup> For the dual die version, the supply current is multiplied by 2.

<sup>&</sup>lt;sup>3</sup> Idle current is the current that is drawn by the IC in the IDLE mode, where it can only receive new commands on the communication bus, but all other blocks are disabled. The analog (excluding the power-on-reset block) is disconnected, only the digital IO part allows clocking of a few vital gates.

<sup>&</sup>lt;sup>4</sup> Standby current corresponds to the current consumed in the digital, where not the main oscillator is running which is used for analog sequencing, but only the low-power oscillator. This standby current is present in Burst mode or WOC mode; whenever the IC is counting down to start a new conversion.

<sup>&</sup>lt;sup>5</sup> Not covered by final test, based on characterization data.

Datasheet

| Parameter           | Symbol | Min. | Тур. | Max. | Unit | Condition   |

|---------------------|--------|------|------|------|------|-------------|

| Leakage Current (5) |        |      |      | 20   | nA   | SDA         |

|                     | Ileak  |      |      | 0.1  | nA   | INT         |

|                     | пеак   |      |      | 25   | nA   | MISO        |

|                     |        |      |      | 20   | nA   | SCLK, MS/CS |

Table 8: Electrical Specification

## 12. Timing Specification

Timing conditions include the variations of supply, temperature and aging, unless specified.

| Parameter                                      | Symbol                  | Min. | Тур.                                           | Max.                 | Unit                | Condition                                                                     |

|------------------------------------------------|-------------------------|------|------------------------------------------------|----------------------|---------------------|-------------------------------------------------------------------------------|

| Main Oscillator Frequency                      | Fosc                    | 0.95 | 1                                              | 1.05                 | MHz                 | T <sub>A</sub> = 35°C                                                         |

| Main Oscillator Thermal Drift                  | F <sub>OSC_TH</sub>     | -5   |                                                | 5                    | %F <sub>osc</sub>   | T <sub>A</sub> within T <sub>AMB</sub>                                        |

| Low Power Oscillator<br>Frequency              | $F_{LPOSC}$             | 48   | 50                                             | 52                   | kHz                 | T <sub>A</sub> = 35°C                                                         |

| LP Oscillator Thermal Drift                    | F <sub>LPOSC_TH</sub>   | -6   |                                                | 6                    | %F <sub>LPOSC</sub> | T <sub>A</sub> within T <sub>AMB</sub>                                        |

| Reset Time (POR and RT command) <sup>(6)</sup> | $T_{POR}$               |      | 1.3                                            | 2.4                  | ms                  | Time from STARTUP to IDLE                                                     |

| Initialization Time <sup>(6)</sup>             | T <sub>INIT</sub>       |      | 165                                            |                      | μs                  | Time from IDLE to start of conversion                                         |

| Voltage Conversion Time (6)                    | $TCONV_V$               | 163  |                                                | 259                  | μs                  | VDD measurement<br>F <sub>OSC</sub> = 1MHz                                    |

| Temperature Conversion<br>Time <sup>(6)</sup>  | TCONV <sub>T</sub>      | 163  |                                                | 835 <sup>(7)</sup>   | μs                  | Programmable Signal Integration Fosc = 1MHz                                   |

| Magnetic Conversion Time (6)                   | $TCONV_M$               | 163  |                                                | 33347 <sup>(8)</sup> | μs                  | Programmable Signal<br>Integration F <sub>OSC</sub> = 1MHz, single<br>channel |

| Conversion Time (6)                            | TCONV                   |      | NV <sub>V</sub> + TCO<br>TCONV <sub>M</sub> +1 | •                    | μs                  | F <sub>OSC</sub> = 1MHz                                                       |

| Output Data Rate (6)                           | $ODR_{DC}$ $ODR_{CONT}$ | 1/   | 1/(TCONV + T <sub>INIT</sub> )<br>1/TCONV      |                      |                     | Duty Cycled Operation Continuous Operation                                    |

| Interval Time <sup>(6)</sup>                   | T <sub>INT</sub>        | 0    |                                                | 1260 <sup>(9)</sup>  | ms                  | Time in between conversion cycles (F <sub>LPOSC</sub> = 50kHz)                |

| Trigger Pulse Width <sup>(6)</sup>             | $T_{TRIG}$              | 0.01 |                                                | 250                  | μs                  | Active High                                                                   |

| Memory Store time (6)                          | T <sub>HS_WAIT</sub>    |      |                                                | 15                   | ms                  | T <sub>A</sub> within T <sub>AMB</sub>                                        |

Table 9: General Timing Specification

<sup>&</sup>lt;sup>6</sup> Not covered by final test, based on characterization data.

$<sup>^{7}</sup>$  (2 $^{\rm OSR2}*96$ )+67. See section 18.4 for more information about filters.

$<sup>^{8}</sup>$   $m*{[(2+2^{DIGFILT})*2^{OSR}*32]+67}, m = selectable 0 to 3 (XYZ) axes. See section 18.4 for more information about filters.$

<sup>&</sup>lt;sup>9</sup> BURST DATA RATE\*20.

## 13. Temperature Specification

The MLX90395 allows for measuring of the junction temperature for on-chip thermal compensations as well as off-chip thermal information within the application, provided there is proper modeling of the junction temperature to application temperature.

| Parameter                        | Symbol           | Min. | Тур. | Max. | Unit                  | Condition               |

|----------------------------------|------------------|------|------|------|-----------------------|-------------------------|

| Temperature Sensor<br>Resolution | $T_{RES}$        |      | 50   |      | LSB <sub>14</sub> /°C |                         |

| Temperature Sensor Output 0°C    | T <sub>0</sub>   |      | 0    |      | LSB <sub>14</sub>     |                         |

| Temperature Sensor Output 35°C   | T <sub>35</sub>  |      | 1750 |      | LSB <sub>14</sub>     | Calibration Temperature |

| Temperature Sensor Linearity     | T <sub>LIN</sub> | -2   |      | +2   | °C                    |                         |

| Temperature Sensor Accuracy      | $T_{ACC}$        | 0    |      | +10  | °C                    | T <sub>A</sub> ≤ 35°C   |

| Temperature Sensor Accuracy      | T <sub>ACC</sub> | -1   |      | +7   | °C                    | T <sub>A</sub> > 35°C   |

Table 10: Temperature Specification

## 14. Voltage Specification

The MLX90395 allows for measurement of the supply voltage for ADC plausibility checks as well as for monitoring battery discharge in battery powered applications.

| Parameter             | Symbol    | Min. | Тур.  | Max. | Unit                 | Condition |

|-----------------------|-----------|------|-------|------|----------------------|-----------|

| Voltage Resolution    | $V_{RES}$ |      | 5500  |      | LSB <sub>16</sub> /V |           |

| Voltage Output for 3V | $V_{3V}$  |      | 16500 |      | LSB <sub>16</sub>    |           |

| Voltage Output for 2V | $V_{2V}$  |      | 11000 |      | LSB <sub>16</sub>    |           |

| Voltage Linearity     | $V_{LIN}$ | -20  |       | 20   | mV                   |           |

| Voltage Accuracy      | $V_{ACC}$ | -200 |       | 200  | mV                   |           |

Table 11: Voltage Specification

## 15. Magnetic Field Requirements

This section describes the magnetic field requirements in order to meet the performance described in section 16.

### 15.1. Medium-Field Variant (-0xx code)

| Parameter                       | Symbol                          | Min. | Тур. | Max.               | Unit | Condition                  |

|---------------------------------|---------------------------------|------|------|--------------------|------|----------------------------|

| Magnetic Flux Density in X or Y | B <sub>X</sub> , B <sub>Y</sub> |      |      | 55 <sup>(10)</sup> | mT   | $\sqrt{B_X^2 + B_Y^2}$     |

| Magnetic Flux Density in Z      | $B_{Z}$                         |      |      | 130                | mT   |                            |

| IMC Gain in X and Y             | $G_{IMC_{XY}}$                  | 1.5  |      | 1.8                |      |                            |

| IMC Gain in Z                   | G <sub>IMC_Z</sub>              | 1    |      | 1.2                |      |                            |

| k factor                        | k                               | 1.3  |      | 1.7                |      | $G_{IMC\_XY} / G_{IMC\_Z}$ |

Table 12: Magnetic field requirement for Medium-Field Variant

## 15.2. High-Field Variant (-1xx code)

| Parameter                       | Symbol                          | Min. | Тур. | Max.                | Unit | Condition                  |

|---------------------------------|---------------------------------|------|------|---------------------|------|----------------------------|

| Magnetic Flux Density in X or Y | B <sub>X</sub> , B <sub>Y</sub> |      |      | 120 <sup>(10)</sup> | mT   | $\sqrt{B_X^2 + B_Y^2}$     |

| Magnetic Flux Density in Z      | $B_{Z}$                         |      |      | 130                 | mT   |                            |

| IMC Gain in X and Y             | $G_{IMC\_XY}$                   | 0.4  |      | 0.6                 |      |                            |

| IMC Gain in Z                   | G <sub>IMC_Z</sub>              | 1.1  |      | 1.2                 |      |                            |

| k factor                        | k                               | 0.3  |      | 0.5                 |      | $G_{IMC\_XY} / G_{IMC\_Z}$ |

Table 13: Magnetic field requirement for High-Field Variant

$<sup>^{10}</sup>$  Above this value, the IMC starts saturating yielding to an increase of the linearity error

## 16. Accuracy Specification

## 16.1. Medium-Field Variant (-0xx code)

Magnetic Specifications (with **Melexis default factory programming**) are valid for temperature range: -40 - 125°C, supply voltage range: 2.6/3.0 - 3.6V unless otherwise noted (condition).

| Parameter                                           | Symbol                                                                                                                | Min.           | Тур.       | Max.              | Unit                                               | Condition                                                                              |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|------------|-------------------|----------------------------------------------------|----------------------------------------------------------------------------------------|

| ADC Internal Resolution                             | N <sub>ADCINT</sub>                                                                                                   |                | 17.2       |                   | bits                                               |                                                                                        |

| ADC External Resolution                             | $N_{ADCEXT}$                                                                                                          |                | 16         |                   | bits                                               |                                                                                        |

| Sensing Range                                       | B <sub>RANGE50</sub>                                                                                                  |                | 50         |                   | mT                                                 |                                                                                        |

| Offset (11)                                         | $X_0, Y_0, Z_0$                                                                                                       | -150           |            | 150               | LSB <sub>16</sub>                                  | T <sub>A</sub> within T <sub>AMB</sub>                                                 |

| Sensitivity X- or Y-axis (12)                       | S <sub>XX50</sub> ,<br>S <sub>YY50</sub>                                                                              |                | 2.5<br>400 |                   | $\mu$ T/LSB <sub>16</sub><br>LSB <sub>16</sub> /mT |                                                                                        |

| Sensitivity Accuracy X- or Y-axis                   |                                                                                                                       | -8             |            | 8                 | %                                                  | T <sub>A</sub> = 35°C                                                                  |

| Sensitivity Temperature<br>Coefficient X- or Y-axis | T <sub>CSXY</sub>                                                                                                     | -500           |            | 500               | ppm/°C                                             | T <sub>A</sub> within T <sub>AMB</sub>                                                 |

| Sensitivity Z-axis (13)                             | S <sub>ZZ50</sub>                                                                                                     |                | 2.5<br>400 |                   | $\mu$ T/LSB <sub>16</sub><br>LSB <sub>16</sub> /mT |                                                                                        |

| Sensitivity Accuracy Z-axis                         |                                                                                                                       | -10            |            | 10                | %                                                  | T <sub>A</sub> = 35°C                                                                  |

| Sensitivity Temperature Coefficient Z-axis          | T <sub>CSZ</sub>                                                                                                      | -600           |            | 600               | ppm/°C                                             | T <sub>A</sub> within T <sub>AMB</sub>                                                 |

| Mismatch on the Raw Signals X, Y and Z $^{(14)}$    | S <sub>MISMXY</sub> S <sub>MISMXZ</sub> S <sub>MISMYZ</sub>                                                           | -2<br>-5<br>-5 |            | 2<br>5<br>5       | %                                                  | T <sub>A</sub> = 35°C                                                                  |

| Thermal Drift of Sensitivity<br>Mismatch            |                                                                                                                       | -3             |            | 3                 | %                                                  | T <sub>A</sub> within T <sub>AMB</sub>                                                 |

| Cross-Axis Sensitivity (intrinsic)                  | S <sub>XYi</sub> , S <sub>YXi</sub> ,<br>S <sub>XZi</sub> , S <sub>ZXi</sub> ,<br>S <sub>YZi</sub> , S <sub>ZYi</sub> | -5             |            | 5                 | %                                                  | T <sub>A</sub> = 35°C                                                                  |

| Noise                                               |                                                                                                                       |                |            | 275<br>350<br>450 | μT rms<br>μT rms<br>μT rms                         | T <sub>A</sub> = 35°C<br>T <sub>A</sub> = 85°C<br>T <sub>A</sub> = 125°C<br>0 μT field |

| Hysteresis                                          |                                                                                                                       |                |            | 60                | LSB <sub>16</sub>                                  | $T_A = 35$ °C                                                                          |

Table 14: Accuracy Specification for Medium-Field Variant

<sup>&</sup>lt;sup>11</sup> The thermal offset drift will be within a +/-30LSB window, by characterization.

<sup>&</sup>lt;sup>12</sup> Sensitivity can be adjusted with the parameter SENSXY, RESX and RESY. See section 18.6 for more details.

<sup>&</sup>lt;sup>13</sup> Sensitivity can be adjusted with the parameter SENSZ and RESZ. See section 18.6 for more details.

<sup>&</sup>lt;sup>14</sup> Die rotation tolerances (tilt die) of +/-2° included.

## 16.2. High-Field Variant (-1xx code)

Magnetic Specifications (with **Melexis default factory programming**) are valid for temperature range: -40 - 125°C, supply voltage range: 2.6/3.0 - 3.6V unless otherwise noted (condition).

| Parameter                                        | Symbol                                                                | Min.           | Тур.        | Max.                 | Unit                                               | Condition                                                                   |

|--------------------------------------------------|-----------------------------------------------------------------------|----------------|-------------|----------------------|----------------------------------------------------|-----------------------------------------------------------------------------|

| ADC Internal Resolution                          | N <sub>ADCINT</sub>                                                   |                | 17.2        |                      | bits                                               |                                                                             |

| ADC External Resolution                          | $N_{ADCEXT}$                                                          |                | 16          |                      | bits                                               |                                                                             |

| Sensing Range                                    | B <sub>RANGE120</sub>                                                 |                | 120         |                      | mT                                                 |                                                                             |

| Offset (15)                                      | $X_0, Y_0, Z_0$                                                       | -150           |             | 150                  | LSB <sub>16</sub>                                  | T <sub>A</sub> within T <sub>AMB</sub>                                      |

| Sensitivity X- or Y-axis (16)                    | S <sub>XX120</sub> ,<br>S <sub>YY120</sub>                            |                | 7.14<br>140 |                      | $\mu$ T/LSB <sub>16</sub><br>LSB <sub>16</sub> /mT |                                                                             |

| Sensitivity Accuracy X- or Y-axis                |                                                                       | -8             |             | 8                    | %                                                  | T <sub>A</sub> = 35°C                                                       |

| Sensitivity Temperature Coefficient X- or Y-axis | $T_{CSXY}$                                                            | -500           |             | 500                  | ppm/°C                                             | T <sub>A</sub> within T <sub>AMB</sub>                                      |

| Sensitivity Z-axis (17)                          | S <sub>ZZ120</sub>                                                    |                | 7.14<br>140 |                      | $\mu$ T/LSB <sub>16</sub><br>LSB <sub>16</sub> /mT |                                                                             |

| Sensitivity Accuracy Z-axis                      |                                                                       | -10            |             | 10                   | %                                                  | T <sub>A</sub> = 35°C                                                       |

| Sensitivity Temperature Coefficient Z-axis       | T <sub>CSZ</sub>                                                      | -600           |             | 600                  | ppm/°C                                             | T <sub>A</sub> within T <sub>AMB</sub>                                      |

| Mismatch on the Raw Signals X, Y and Z $^{(18)}$ | S <sub>MISMXY</sub> S <sub>MISMXZ</sub> S <sub>MISMYZ</sub>           | -2<br>-5<br>-5 |             | 2<br>5<br>5          | %                                                  | T <sub>A</sub> = 35°C                                                       |

| Thermal Drift of Sensitivity<br>Mismatch         |                                                                       | -3             |             | 3                    | %                                                  | T <sub>A</sub> within T <sub>AMB</sub>                                      |

| Cross-Axis Sensitivity (intrinsic)               | $S_{XYi}$ , $S_{YXi}$ , $S_{XZi}$ , $S_{ZXi}$ , $S_{YZi}$ , $S_{ZYi}$ | -5             |             | 5                    | %                                                  | T <sub>A</sub> = 35°C                                                       |

| Noise                                            |                                                                       |                |             | 1080<br>1250<br>1650 | μT rms<br>μT rms<br>μT rms                         | $T_A = 35$ °C<br>$T_A = 85$ °C<br>$T_A = 125$ °C<br>$0 \mu T \text{ field}$ |

| Hysteresis                                       |                                                                       |                |             | 60                   | LSB <sub>16</sub>                                  | T <sub>A</sub> = 35°C                                                       |

Table 15: Accuracy Specification for High-Field Variant

\_\_\_

<sup>&</sup>lt;sup>15</sup> The thermal offset drift will be within a +/-30LSB window, by characterization.

<sup>&</sup>lt;sup>16</sup> Sensitivity can be adjusted with the parameter SENSXY, RESX and RESY. See section 18.6 for more details.

$<sup>^{17}</sup>$  Sensitivity can be adjusted with the parameter SENSZ and RESZ. See section 18.6 for more details.

<sup>&</sup>lt;sup>18</sup> Die rotation tolerances (tilt die) of  $\pm$ -2° included.

### 17. Functional Description

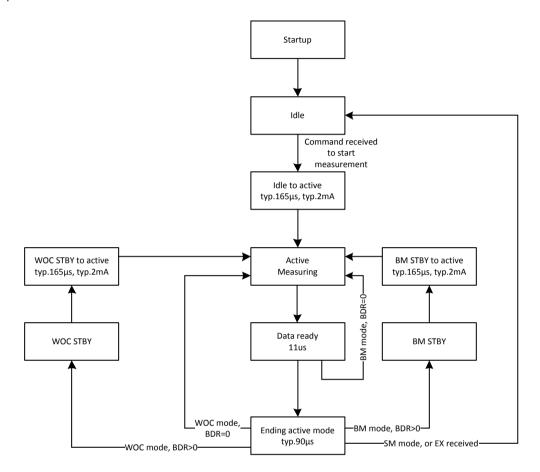

#### 17.1. Operating Modes

The MLX90395 always acts as slave on the bus. It operates with 3 state machines:

- Measurement State Machine running off the Main Oscillator

- Low Power State Machine running off the Low Power Oscillator

- Communication State Machine running off the bus clock

The three operating modes are controlled and defined by the master. All modes can be enabled and disabled at runtime through the communication protocol. On reset, the device is in idle mode, waiting for commands.

The components (field in X, Y or Z direction, temperature and voltage) which are needed to be measured can be provided when sending the commands. The order of conversion is fixed, and components which are not needed are simply skipped.

It is the user's responsibility to read back the data and ensure that timings are met. The MLX90395 is purely a slave. Even in burst mode, the user is responsible to collect the data from the MLX90395.

| Operating<br>Mode                  | Start of Mode                   | End of Mode<br>(Return to IDLE) | Measurement Data                                                                                                                                                  |

|------------------------------------|---------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single<br>Measurement              | SM command  TRG pin rising edge | Measurement<br>finished         | Argument of SM command or BURST_SEL register content if empty argument BURST_SEL register if empty argument, provided SM command has been issued once in the past |

| Burst Mode                         | SB command                      | EX command                      | Argument of SB command or BURST_SEL register content if empty argument                                                                                            |

| Wake-up On<br>Change<br>(WOC) Mode | SWOC<br>command                 | EX command                      | Argument of SWOC command or BURST_SEL register content if empty argument                                                                                          |

Table 16: Summary of the operating modes

### 17.1.1. Single Measurement

In single measurement mode, a single measurement is requested by the master through either the SM command or via a rising edge on the TRG pin. After finishing the measurement, the INT pin will go high and the MLX90395 will go back to idle mode. The measurement can be read out at any time by means of the RM command. This will clear the INT pin.

#### 17.1.2. Burst Mode

In burst mode, the MLX90395 will continuously make measurements. The mode is started with the SB command and can be ended with the EX command. Measurements are read by the RM command and the status byte will indicate the freshness of the data. The rate of measurements is programmable. Each time a measurement is finished, the INT pin will go high. Reading out the data will clear the INT pin. If the measurement is not read on time, it will be overwritten by the next measurement when ready. The INT pin will show again a rising edge when the set of measurements can be read out. As long as the INT pin is high, the data is ensured to be most recent and ready.

Datasheet

In burst mode, the only allowed commands are RM and EX. In case a different command is sent, the status will show a communication error. In case of SPI, this status is sent right after the first byte is received (even for multi byte commands).

#### 17.1.3. Wake-up on Change Mode

In wake-up on change mode, the MLX90395 will continuously make measurements. The mode is started with the SWOC command and can be ended with the EX command. Measurements can be read by the RM command, and the status byte will indicate the freshness of the data. Also here the rate of measurements is programmable. This mode differs from the burst mode in the sense that the INT pin will not go high at each finish of measurements but go high only when a specific condition is met. This condition can be controlled by the user:

- Absolute mode: each measurement is compared with the initial one (first measurement after start of the WOC mode). If the difference is larger than the threshold, then the INT pin goes high. The pin is cleared by the RM command.

- Differential mode: each measurement is compared with the previous one. If the difference is larger than the threshold, then the INT pin goes high. The pin is cleared by the RM command.

Comparisons are done on the 16-bit output data, independent of the resolution programmed.

In WOC mode, the only allowed commands are RM and EX. In case a different command is sent, the status will show a communication error. In case of SPI, this status is sent right after the first byte is received (even for multi byte commands).

#### 17.2. Flow Chart

The flow chart below shows the different states the sensor can be in and how they are related for different measurement types. In case of an exit command, the measurement is first finished, and the loop is ended via the SM path.

Figure 4: Flow Chart (BDR = BurstDataRate)

#### 17.3. Status Byte

A status byte is provided on nearly each command (RT does not return a status byte). Depending on the operating mode, the interpretation differs.

| Mode       | Bit7 | Bit6 | Bit5       | Bit4  | Bit3     | Bit2 | Bit1 | Bit0 |

|------------|------|------|------------|-------|----------|------|------|------|

| Burst Mode | 1    | Meas | urement Co | unter | CE / DED | OVF  | RST  | DRDY |

| WOC Mode   | 0    | 1    | 0          | 0     | CE / DED | OVF  | RST  | DRDY |

| SM Mode    | 0    | 0    | 1          | 0     | CE / DED | OVF  | RST  | DRDY |

| Idle       | 0    | 0    | 0          | 0     | CE / DED | OVF  | RST  | DRDY |

| Memory     | 0    | 0    | 0          | 0     | CE / DED | SEC  | RST  | DRDY |

Table 17: Status Byte

The SB command is always replied with a "Burst Mode" status, the SWOC command by a "WOC Mode" status. When the SM command is successfully received, an "SM Mode" status is given.

For the RM and RV command, the status returned purely depends on the mode in which the IC is operating. For single measurement mode, if the measurement is finished, the "Idle" status byte is given.

An EX command, when successfully received is replied with an "Idle" status byte.

Memory commands (HR, HS, RR and WR) are replied with the "Memory" status byte.

In case of an illegal command (RR in burst mode for example) then the status will be the one of the mode currently in, not necessarily the one associated with the command. The command got rejected, and the CE bit is set.

Melexis recommends verifying that the status byte matches the expected value.

#### 17.3.1. Data Ready - DRDY

This flag is set to 1 to indicate that new data is ready (not yet read), or when it is the first time that this data is being read. This flag is updated after the measurement is done.

In burst mode, there is a 10µs window just before the measurement (and measurement counter) is updated, where the flag is always zero, even if the data has not yet been read.

#### 17.3.2. Reset - RST

The reset flag is set whenever the IC has gone through a power-on reset (cold reset through VDD cycling or warm reset through RT command).

#### 17.3.3. Single Bit Error Corrected - SEC

If set, a single bit error is detected in the NVRAM, and the bit is corrected.

#### 17.3.4. Double Bit Error Detected - DED

If set, a double bit error is detected in the NVRAM. Once this bit is set, it will be latched until the problem is cleared (eg. by a write operation to the inconsistent register).

Datasheet

#### 17.3.5. Overflow - OVF

If set, it indicates that the MSBit of the ADC (bit 18) is set. This situation should not occur, and could indicate a failure in the analog front-end of the IC.

#### 17.3.6. Communication Error - CE

This flag is set in case a communication error is detected. It can be that a wrong command is set (or too early), or a command which was not allowed on a specific operating mode.

#### 17.3.7. Measurement Counter

The 3-bit measurement counter is present in burst mode and is increased on each measurement. This allows the user to know if a measurement is missed when for example the RM commands are not in sync with the measurement rate.

#### 17.4. Measurement CRC

The measured data is protected with a CRC in order to provide a data integrity check at master side. The CRC is implemented as 8-bit CRC-8-CCITT (polynomial 0x07) on the totality of the measured data. The calculation is always done with 10 bytes of data in the order X[15:8], X[7:0], Y[15:8], Y[7:0], Z[15:8], Z[7:0], T[15:8], V[7:0]. Components which are not measured are to be filled out with 0x00.

#### 17.4.1. CRC calculation

The below describes the CRC calculation. Also an example is provided to show the CRC calculation in action.

```

// Code

// Example

crc = 0x00;

crc = 0x00;

crc = CRC_TABLE[crc ^ X[15:8]];

0x00 = CRC\_TABLE[0x00 ^ 0x00];

crc = CRC_TABLE[crc ^ X[7:0]];

0x00 = CRC\_TABLE[0x00 ^ 0x00];

crc = CRC_TABLE[crc ^ Y[15:8]];

0x89 = CRC\_TABLE[0x00 ^ 0x80];

0xB6 = CRC_TABLE[0x89 ^ 0x00];

crc = CRC_TABLE[crc ^ Y[7:0]];

crc = CRC_TABLE[crc ^ Z[15:8]];

0x0B = CRC\_TABLE[0xB6 ^ 0x00];

crc = CRC_TABLE[crc ^ Z[7:0]];

0x31 = CRC_TABLE[0x0B ^ 0x00];

crc = CRC_TABLE[crc ^ T[15:8]];

0x8C = CRC_TABLE[0x31 ^ 0x05];

crc = CRC_TABLE[crc ^ T[7:0]];

0x5F = CRC_TABLE[0x8C ^ 0x26];

crc = CRC

TABLE[crc ^ V[15:8]];

0x9A = CRC_TABLE[0x5F ^ 0x00];

crc = CRC_TABLE[crc ^ V[7:0]];

0xCF = CRC_TABLE[0x9A ^ 0x00];

```

#### The CRC table is shown below

```

CRC_TABLE[256] = {

0x00, 0x07, 0x0E, 0x09, 0x1C, 0x1B, 0x12, 0x15,

0x38, 0x3F, 0x36, 0x31, 0x24, 0x23, 0x2A, 0x2D,

0x70, 0x77, 0x7E, 0x79, 0x6C, 0x6B, 0x62, 0x65,

0x48, 0x4F, 0x46, 0x41, 0x54, 0x53, 0x5A, 0x5D,

0xE0, 0xE7, 0xEE, 0xE9, 0xFC, 0xFB, 0xF2, 0xF5,

0xD8, 0xDF, 0xD6, 0xD1, 0xC4, 0xC3, 0xCA, 0xCD,

0x90, 0x97, 0x9E, 0x99, 0x8C, 0x8B, 0x82, 0x85,

0xA8, 0xAF, 0xA6, 0xA1, 0xB4, 0xB3, 0xBA, 0xBD,

0xC7, 0xC0, 0xC9, 0xCE, 0xDB, 0xDC, 0xD5, 0xD2,

0xFF, 0xF8, 0xF1, 0xF6, 0xE3, 0xE4, 0xED, 0xEA,

0xB7, 0xB0, 0xB9, 0xBE, 0xAB, 0xAC, 0xA5, 0xA2,

0x8F, 0x88, 0x81, 0x86, 0x93, 0x94, 0x9D, 0x9A,

0x27, 0x20, 0x29, 0x2E, 0x3B, 0x3C, 0x35, 0x32,

0x1F, 0x18, 0x11, 0x16, 0x03, 0x04, 0x0D, 0x0A,

0x57, 0x50, 0x59, 0x5E, 0x4B, 0x4C, 0x45, 0x42,

0x6F, 0x68, 0x61, 0x66, 0x73, 0x74, 0x7D, 0x7A,

0x89, 0x8E, 0x87, 0x80, 0x95, 0x92, 0x9B, 0x9C,

0xB1, 0xB6, 0xBF, 0xB8, 0xAD, 0xAA, 0xA3, 0xA4,

0xF9, 0xFE, 0xF7, 0xF0, 0xE5, 0xE2, 0xEB, 0xEC,

0xC1, 0xC6, 0xCF, 0xC8, 0xDD, 0xDA, 0xD3, 0xD4,

0x69, 0x6E, 0x67, 0x60, 0x75, 0x72, 0x7B, 0x7C,

0x51, 0x56, 0x5F, 0x58, 0x4D, 0x4A, 0x43, 0x44,

0x19, 0x1E, 0x17, 0x10, 0x05, 0x02, 0x0B, 0x0C,

0x21, 0x26, 0x2F, 0x28, 0x3D, 0x3A, 0x33, 0x34,

0x4E, 0x49, 0x40, 0x47, 0x52, 0x55, 0x5C, 0x5B,

0x76, 0x71, 0x78, 0x7F, 0x6A, 0x6D, 0x64, 0x63,

0x3E, 0x39, 0x30, 0x37, 0x22, 0x25, 0x2C, 0x2B,

0x06, 0x01, 0x08, 0x0F, 0x1A, 0x1D, 0x14, 0x13,

0xAE, 0xA9, 0xA0, 0xA7, 0xB2, 0xB5, 0xBC, 0xBB,

0x96, 0x91, 0x98, 0x9F, 0x8A, 0x8D, 0x84, 0x83,

OxDE, OxD9, OxD0, OxD7, OxC2, OxC5, OxCC, OxCB,

0xE6, 0xE1, 0xE8, 0xEF, 0xFA, 0xFD, 0xF4, 0xF3

```

#### 17.5. Commands

In the commands with zyxt in their first byte, the zyxt is used to select which components need to be measured (set corresponding bit to 1). zyxt = 0x0 results in all components being measured according the settings of VmeasEn and BurstSel (X, Y, Z, T and V). Else, the components of the zyxt argument are measured. With temperature compensation enabled, the temperature will always be measured. However depending on the argument zyxt, it can be read out or not (for CRC calculation it will be 0x0). Recommended is to do the measurement and the read command with the same zyxt argument.

It is <u>not</u> allowed to use the Reset command (RT) during any mode (Single Measurement Mode, Burst Mode, WOC Mode). The Exit Mode command (EX) has to be used to end a mode. The Reset command can be applied at least 1ms following the Exit command, if required.

| Name                          | Symbol | # | CMD Byte #1                 | CMD Byte #2   | CMD Byte #3 | CMD Byte #4   |

|-------------------------------|--------|---|-----------------------------|---------------|-------------|---------------|

| Start Burst Mode              | SB     | 1 | 0b0001 zyxt                 | N/A           | N/A         | N/A           |

| Start WOC Mode                | SWOC   | 2 | 0b0010 zyxt                 | N/A           | N/A         | N/A           |

| Start Single Measurement Mode | SM     | 3 | 0b0011 zyxt                 | N/A           | N/A         | N/A           |

| Read Measurement (SPI)        | RM     | 4 | 0b0100 zyxt                 | N/A           | N/A         | N/A           |

| Read Register (SPI)           | RR     | 5 | 0b0101 dddd <sup>(19)</sup> | REG[5:0] << 2 | N/A         | N/A           |

| Write Register (SPI)          | WR     | 6 | 0b0110 dddd <sup>(19)</sup> | DATA[15:8]    | DATA[7:0]   | REG[5:0] << 2 |

| Exit Mode                     | EX     | 8 | 0b1000 0000                 | N/A           | N/A         | N/A           |

| Read Voltage                  | RV     | С | 0b1100 dddd <sup>(19)</sup> | N/A           | N/A         | N/A           |

| Memory Recall                 | HR     | D | 0b1101 dddd <sup>(19)</sup> | N/A           | N/A         | N/A           |

| Memory Store                  | HS     | Ε | 0b1110 dddd <sup>(19)</sup> | N/A           | N/A         | N/A           |

| Reset                         | RT     | F | 0b1111 0000                 | N/A           | N/A         | N/A           |

Table 18: Command overview

Register access is always done per word (=2 bytes).

In SPI commands, the register equals the word-address, and is shifted by two bits to the left. To access register 0x01, the corresponding command byte becomes 0x04.

For I<sup>2</sup>C, the RR and WR commands do not exist, but direct register access is available through the I<sup>2</sup>C protocol. More information is found in section 17.7.

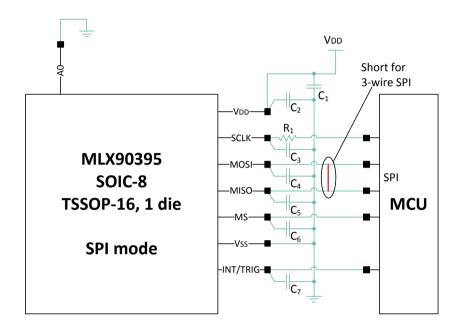

#### 17.6. SPI Communication

The SPI protocol is of mode 3, which means that data is clocked on rising edge of the clock and the clock is at a high level in idle (CPOL=1, CPHA=1). MSbits are sent first. CS must be high after command completion and whenever the IC is not communicated with. With CS low the IC will wait for communication to occur.

Note that MISO and MOSI can be shorted together to allow for 3-wire SPI (mind the increased capacitance). This implies that the SPI output of MLX90395 is half-duplex. There is one danger, in case of an illegal command with more than 1 command byte, the IC immediately sends out the status byte after receiving the

$<sup>^{19}</sup>$  d stands for "don't care". These bits are not checked and can be both 0 and 1.

Datasheet

first byte. This leads to a collision on the bus. Illegal commands like this are RR and WR in burst or WOC mode. Always allow the current measurement to be finished too after sending the EX command, before sending other commands.

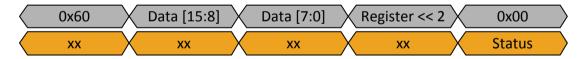

### 17.6.1. Command implementation

For the examples give, the below convention is used.

Figure 5: SPI convention

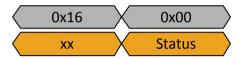

#### 17.6.1.1. SB, SWOC, SM, EX, HR, HS

All the commands follow the structure below. The reply from the MLX90395 is only the status byte. The example below is for a start of a burst mode with X and Y being measured.

Figure 6: SB command, XY

After the HS command, wait at least 15ms before sending the next command to allow the IC to update the NVRAM correctly.

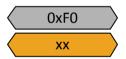

#### 17.6.1.2. RT

This command will (warm-)reset the IC. The status byte of the command following will indicate the reset event.

Figure 7: RT command

#### 17.6.1.3. RM

This command differs depending on the value for zyxt. In case it is different than 0, the data is returned in the order Status-T-X-Y-Z-CRC, where the components which are set to zero are skipped. In case zyxt is 0, the returned order is Status-CRC-X-Y-Z-T-V (none skipped, unmeasured data is set to 0). The below three examples show this.

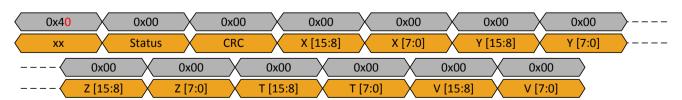

Figure 8: RM command, XYZTV

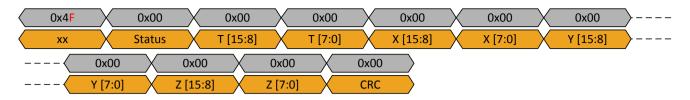

Figure 9: RM command, XYZT

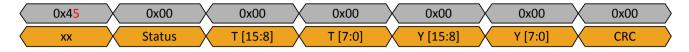

Figure 10: RM command, YT

#### 17.6.1.4. RR

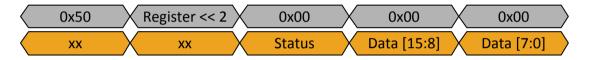

Important in this command is that the register address to be read needs to be shifted left by two bits. To read register 0x12 for example, the MOSI byte becomes 0x48.

Figure 11: RR command

#### 17.6.1.5. WR

Important in this command is that the register address to be read needs to be shifted left by two bits. To read register 0x12 for example, the MOSI byte becomes 0x48.

Figure 12: WR command

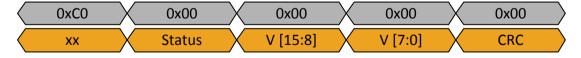

#### 17.6.1.6. RV

In case RM with 0 as zyxt is done, V can be returned. To get the data faster without the X, Y, Z and T (all zero) also being clocked out, the RV command can be used.

Figure 13: RV command

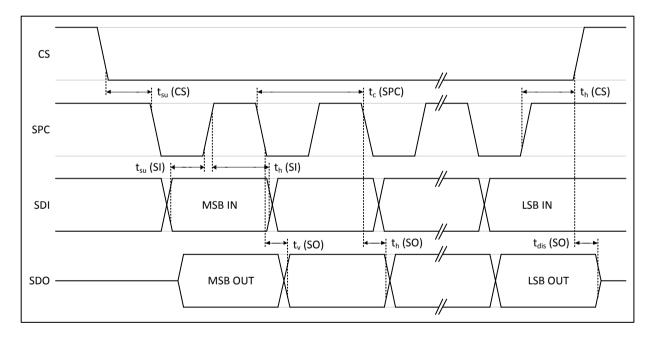

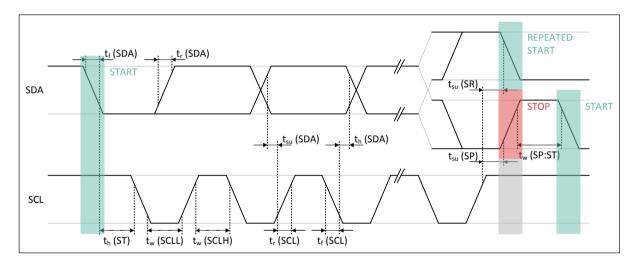

## 17.6.2. SPI Timing Specification

All timings are referred to the levels found in Table 8.

| Electrical Parameter    | Symbol                | Min. | Max. | Unit |

|-------------------------|-----------------------|------|------|------|

| SPI Clock Cycle         | t <sub>c</sub> (SPC)  | 100  |      | ns   |

| SPI Clock Cycle         | t <sub>c</sub> (SPC)  |      | 10   | MHz  |

| CS Setup Time           | t <sub>su</sub> (CS)  | 5    |      | ns   |

| CS Hold Time            | t <sub>h</sub> (CS)   | 10   |      | ns   |

| SDI Input Setup Time    | t <sub>su</sub> (SI)  | 5    |      | ns   |

| SDI Input Hold Time     | t <sub>h</sub> (SI)   | 15   |      | ns   |

| SDO Valid Output Time   | t <sub>v</sub> (SO)   |      | 50   | ns   |

| SDO Output Hold Time    | t <sub>h</sub> (SO)   | 5    |      | ns   |

| SDO Output Disable Time | t <sub>dis</sub> (SO) |      | 50   | ns   |

Table 19: General SPI Timing Specification

Figure 14: SPI Timing Diagram

## 17.6.3. EMC filter (not re-programmable) - Not available in BAA version

An RC filter is enabled on the SPI communication input lines. The impact of this filter is that 1MHz is the maximum SPI clock frequency that the IC accepts. For other filter configurations, please contact Melexis.

| Parameter                | Symbol      | Min. | Тур. | Max. | Unit | Condition |

|--------------------------|-------------|------|------|------|------|-----------|

| SCLK RC Filter Bandwidth | $BW_{1MHz}$ | 2    |      | 4    | MHz  |           |

| CS RC Filter Bandwidth   | $BW_{CS}$   | 3.6  |      | 9.5  | MHz  |           |

| MOSI RC Filter Bandwidth | $BW_{MOSI}$ | 4.75 |      | 9.15 | MHz  |           |

Table 20: SPI RC Filter Specifications

This feature is **not available in the BAA** version.

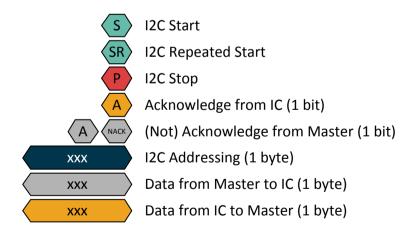

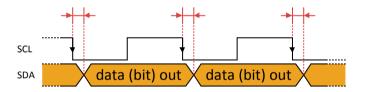

## 17.7. I<sup>2</sup>C Communication

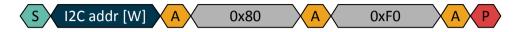

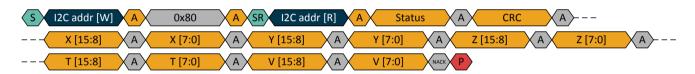

The I<sup>2</sup>C protocol is implemented such that the command is written to a specific register (0x80) in the RAM, and the status and measurement data are read back from this RAM. The commands themselves are the same as for SPI (section 17.5) except for the read measurement commands and the memory read/write commands. For memory read/write commands, register access is provided directly through the I<sup>2</sup>C protocol. Note that memory read/write commands are required to be word-wise, so always in multiples of 2 bytes. The I2C protocol uses the byte address instead of the word address. Because a word contains 2 bytes, the byte address is double that of the word address or register. Hence in the I<sup>2</sup>C, the corresponding command byte becomes the register shifted by 1 bit to the left.

Read measurement is the same as a memory read, except starting from the status register. MSbits are sent first.

The 7-bit I<sup>2</sup>C-address is determined by the connection to the A0 and A1 pins. The 5 MSBs are programmed by Melexis in the MLX90395. Please contact Melexis in case other addressing is required.